模数转换器(ADC)基础概念理解

模数转换器(ADC)基础概念理解

摘要

模数转换器(Analog-to-Digital Converter, ADC)作为连接物理模拟世界与数字计算系统的核心接口,其技术体系深度横跨微电子学、信号处理理论与微波电路设计。本文从全方位、极深度的视角系统梳理 ADC 的技术脉络:首先追溯其从真空管到智能集成的工艺演进历史;其次,深度解剖逐次逼近型(SAR)、Σ-Δ 调制型、流水线型(Pipeline)三大主流架构的核心电路拓扑、数学功耗模型及性能优化路径,并辅以详尽的列表对比分析;第三,创新性地横向盘点了涵盖压控振荡器型(VCO-based)、时间编码型、循环型等 8 种特种与前沿 ADC 拓扑,填补了常规架构认知的盲区;第四,结合工业、医疗、5G 通信等真实场景,给出 PCB 级信号完整性(SI/PI)的严谨工程设计指南。

关键词:ADC;模数转换器;功耗模型;特种拓扑

引言

在数字化浪潮席卷全球的背景下,ADC 作为模拟信号数字化的“核心技术咽喉”,已深刻渗透至工业自动化、6G 通信、医疗影像、自动驾驶雷达等现代电子领域。ADC 的核心使命在于将物理世界连续变化的模拟量(电压、电流、温度等)无损、高效地转换为数字系统可处理的离散代码。

然而,ADC 的设计与应用是一门在速度(带宽)、精度(分辨率)与功耗构成的“不可能三角”中进行极致权衡的工程艺术。现有文献往往存在局限性:部分侧重主流架构的泛泛概念而缺乏电路与功耗的深度模型,部分忽视了在极端应用场景下大放异彩的特种拓扑,更鲜有文章将系统级 PCB 设计与底层的物理数学公式融会贯通。基于此,本文以严谨的专业标准,为您重构 ADC 的全维度认知体系。

1. ADC 的技术演进历程与底层逻辑

1 ADC的技术演进与原理基础

1.1 技术演进历程:从笨重到智能的跨越

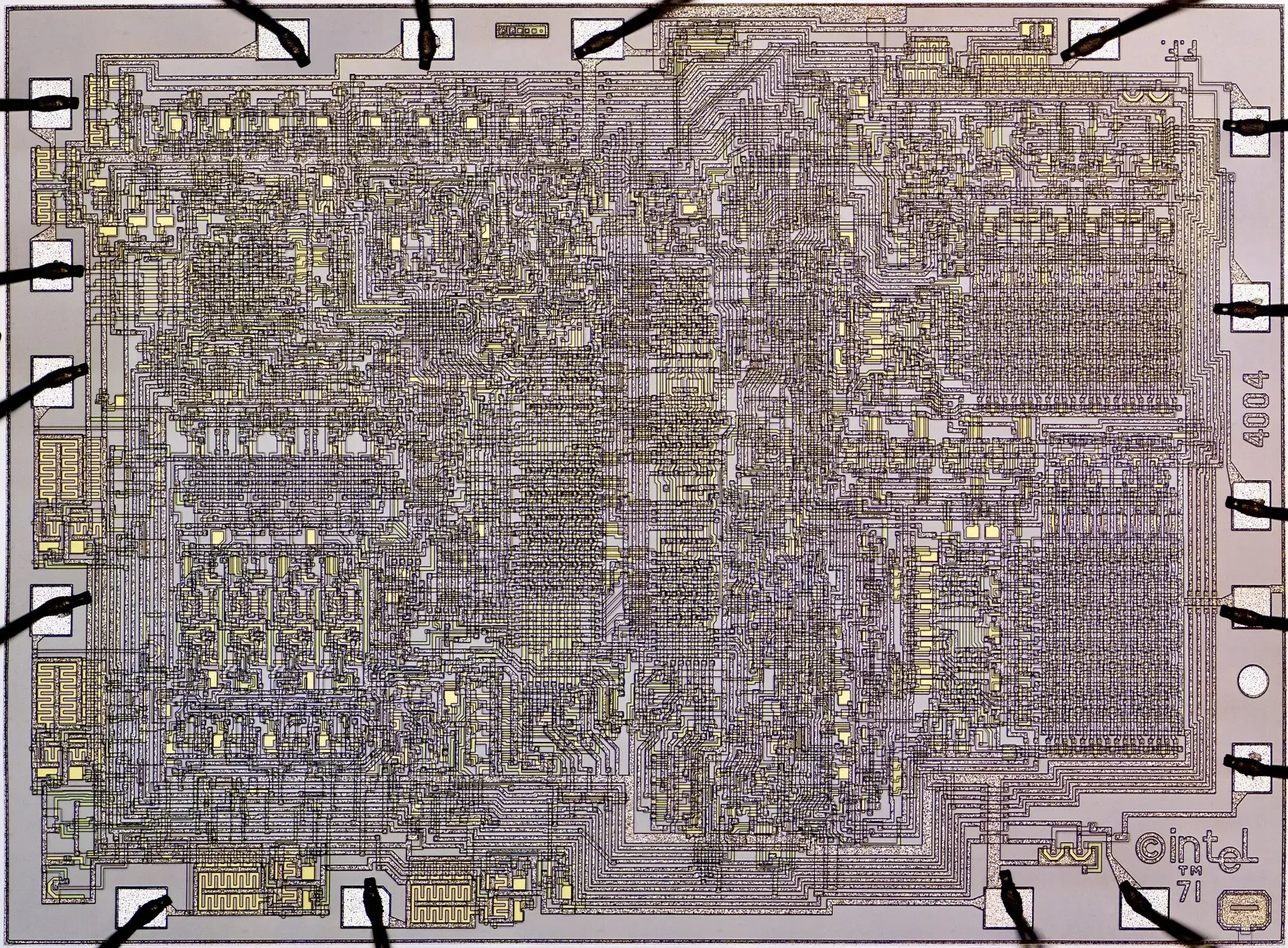

ADC的发展与微电子工艺、信号处理理论的进步深度绑定,其演进路径清晰呈现为”原理奠基-架构分化-集成革新-智能优化”四个阶段,各阶段的核心特征、工艺支撑与性能突破如表1所示。

表1 ADC技术演进阶段及核心特征

| 发展阶段 | 时间范围 | 核心工艺 | 关键突破 | 性能特征(精度/速度/功耗) |

|---|---|---|---|---|

| 原理奠基期 | 1940s-1960s | 真空管、分立元件 | 奈奎斯特定理、PCM理论、SAR/Σ-Δ雏形 | 11位分辨率、50 kSPS采样率、功耗500W(真空管SAR) |

| 架构分化期 | 1970s-1980s | BJT、早期CMOS | 闪存/积分型/子范围架构出现、误差校正技术 | 8-12位分辨率、1 MSPS采样率、功耗10-100mW(BJT SAR) |

| 集成革新期 | 1990s-2010s | 成熟CMOS | 单片集成、时间交织技术、开关电容DAC | 16-24位分辨率、100 MSPS采样率、功耗1-10mW(CMOS Σ-Δ) |

| 智能优化期 | 2010s至今 | FinFET、BiCMOS | 混合架构、自适应校准、忆阻器融合 | 24位+分辨率、GSPS级采样率、功耗μW级(物联网低功耗ADC) |

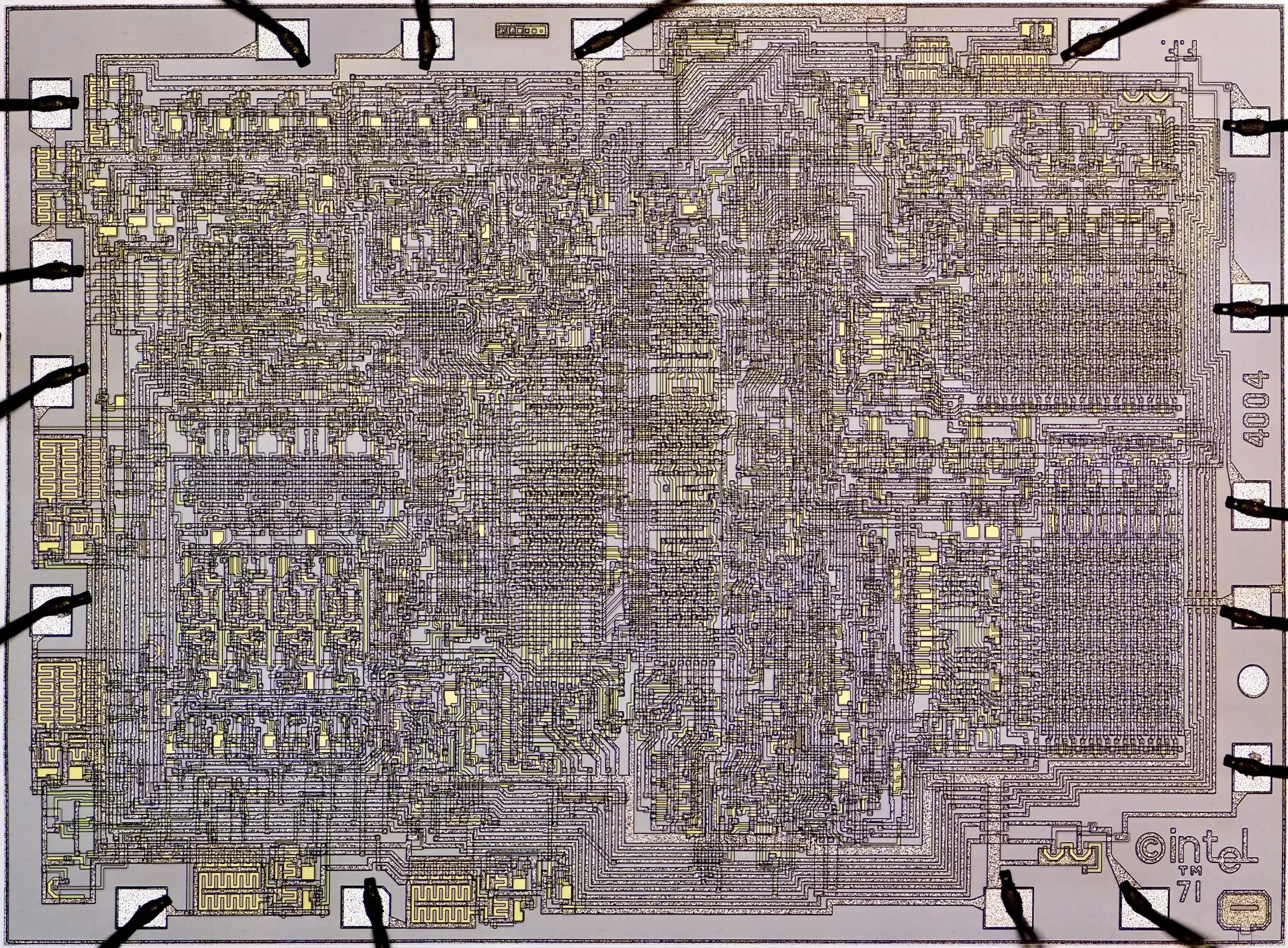

1.1.1 原理奠基期(1940s-1960s)

核心贡献是建立ADC的基础理论体系与原型实现:1940年代贝尔实验室提出脉冲编码调制(PCM)理论,首次将逐次逼近算法用于模拟-数字转换;1954年Epsco推出首款商用真空管SAR ADC,实现11位分辨率,但体积庞大、功耗高达500W;同期奈奎斯特采样定理确立,明确了采样率与信号带宽的基本关系(),为后续ADC设计提供理论准则;1950年代末,Σ-Δ调制的核心概念(过采样与噪声整形)被提出,为高精度ADC设计奠定理论基础。

1.1.2 架构分化期(1970s-1980s)

BJT与早期CMOS工艺推动ADC向模块化、多架构方向发展:闪存ADC凭借并行比较架构实现纳秒级转换速度,主导雷达、视频等高速领域,但比较器数量随分辨率指数增长(),功耗与成本居高不下;积分型(双斜率)ADC依托抗干扰优势成为数字万用表的首选,其积分过程可抑制工频干扰;子范围架构(流水线前身)通过分阶段转换实现速度与精度的初步平衡;SAR ADC则凭借中等速度与低功耗,成为数据采集系统的主力,AD574作为该阶段的标杆器件,通过激光修调薄膜电阻DAC实现12位高精度。此阶段确立了”速度-精度-功耗”的三维权衡思路,架构分化适配不同场景需求。

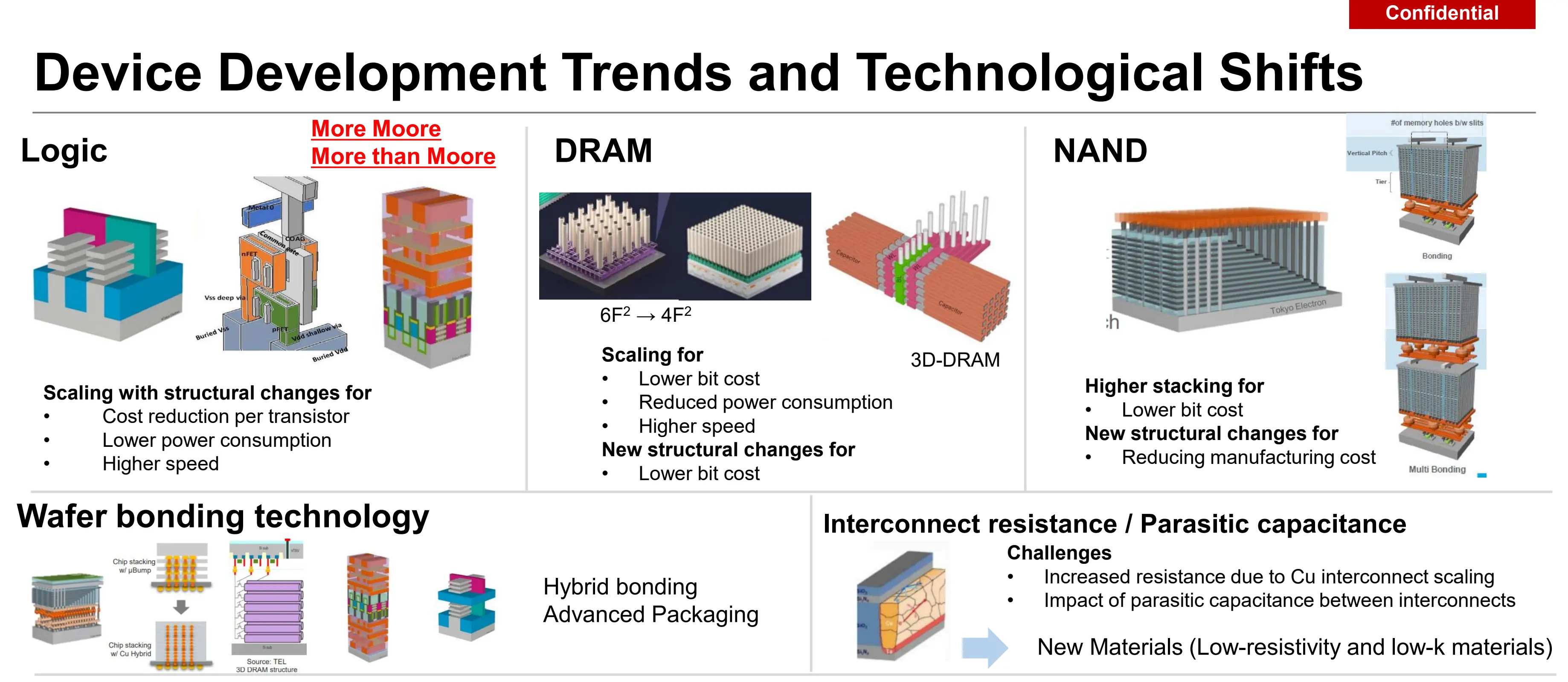

1.1.3 集成革新期(1990s-2010s)

CMOS工艺的成熟实现了模拟与数字电路的单片集成,推动ADC性能飞跃:Σ-Δ ADC集成数字滤波与抽取模块,解决了早年数字复杂度高的痛点,实现16-24位超高分辨率;SAR ADC采用开关电容DAC替代激光修调电阻,通过高精度光刻实现电容匹配,兼顾精度与成本,功耗降至毫瓦级;流水线ADC加入轨道保持电路与误差校正技术,1.5位/级架构成为标准设计,有效抑制失码;时间交织技术突破单通道速度极限,通过多通道并行采样实现GSPS级采样率,满足高速通信需求。

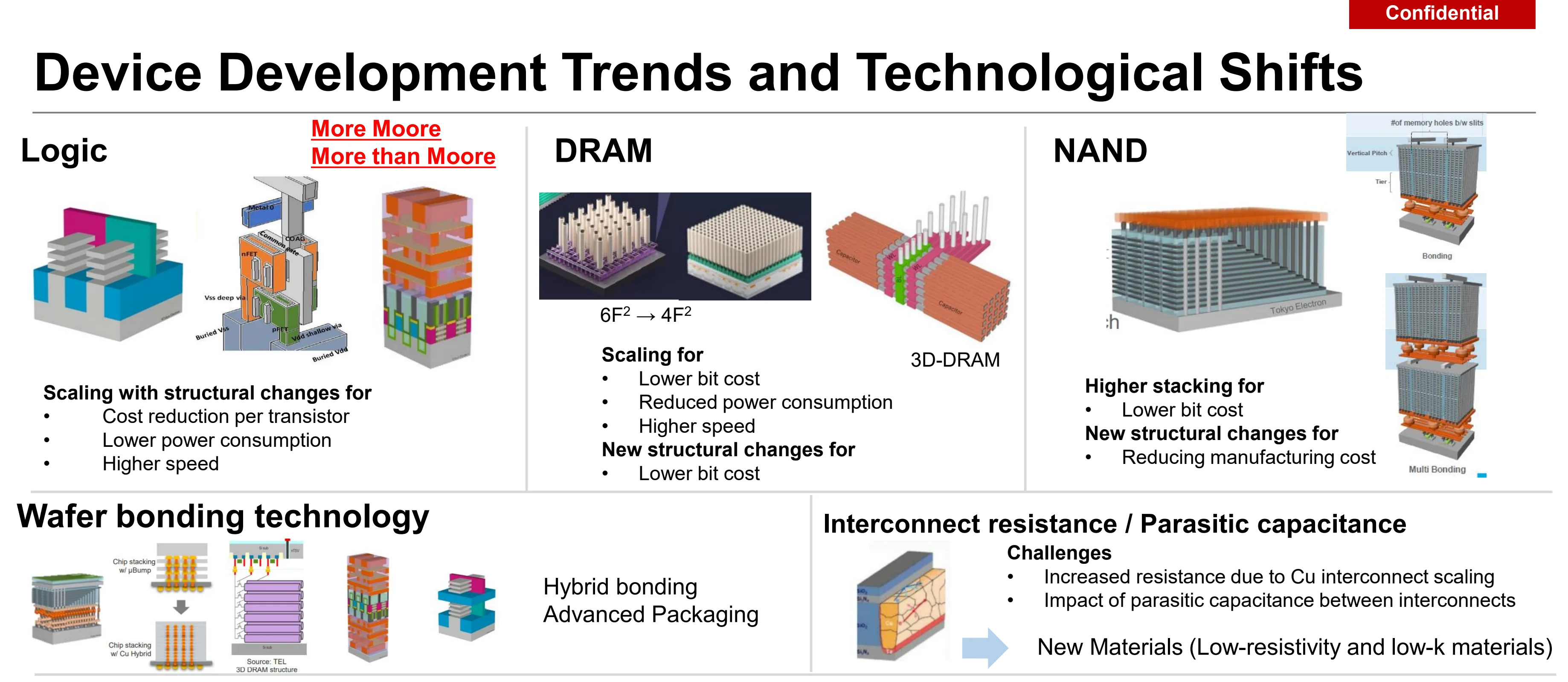

1.1.4 智能优化期(2010s至今)

先进工艺与智能算法的融合推动ADC向高集成、低功耗、自适应方向发展:16nm FinFET工艺使SAR ADC功耗降低50%,泄漏电流控制在nA级;SAR-流水线、Σ-Δ-SAR等混合架构兼顾多维度性能,如SAR-流水线ADC实现14位分辨率、100 MSPS采样率,同时保持低延迟;片上自适应校准算法实时补偿温度、电压漂移,将INL/DNL控制在0.1 LSB以内;忆阻器融合架构使ADC能耗锐减57.2%;低功耗技术突破使物联网应用的ADC功耗降至μW级,休眠功耗甚至低至nW级。

1.2 核心工作原理:采样-量化-编码三步骤

无论架构如何演变,ADC的核心工作流程均遵循”采样-量化-编码”三个基本步骤,其原理本质是将连续的模拟信号离散化为数字代码,各步骤的专业设计要点如下:

1.2.1 采样

采样是将连续时间信号转换为离散时间信号的过程,核心技术要求包括:

- 奈奎斯特采样定理:采样率()需至少为输入信号最高频率()的2倍(),否则会出现混叠失真,实际工程中通常取以预留滤波余量;

- 采样保持电路(SHA):由采样开关、保持电容与缓冲放大器组成,关键参数包括建立时间()、孔径抖动()、输入带宽();

- 采样开关优化:采用Bootstrapped开关(自举开关)消除MOS管阈值电压对采样线性度的影响,导通电阻()可控制在100Ω以内;

- 孔径抖动影响:时钟抖动会导致采样电压误差,高频信号下误差公式为,需将抖动控制在ps级以保证高精度采样。

1.2.2 量化

量化是将采样得到的连续电压值映射到离散量化电平的过程,核心数学模型与技术要点包括:

- 量化电平数:由ADC分辨率()决定,共个量化电平,相邻量化电平的间隔为最小有效位(LSB),公式为(FSR为满量程范围);

- 量化误差:固有误差,理想情况下误差范围为,均方根值为,无法通过校准消除,只能通过提升分辨率或过采样抑制;

- 量化类型:分为均匀量化(线性ADC)与非均匀量化(压缩扩展ADC,如A律/μ律PCM),前者适用于工业测量,后者适用于语音通信;

- 过采样量化:Σ-Δ ADC通过过采样率(OSR)提升量化精度,信噪比提升公式为,2阶调制器可实现。

1.2.3 编码

编码是将量化后的离散电平转换为二进制代码(或其他数字编码形式)的过程,不同架构的编码方式差异显著:

- SAR ADC:通过逐位比较生成自然二进制码,转换时间为个时钟周期;

- Σ-Δ ADC:先输出1位数字流,再通过数字滤波与抽取编码为高分辨率二进制码,存在滤波器建立延迟;

- 流水线ADC:通过多级级联编码合成最终输出,存在级流水线延迟;

- 编码格式:包括自然二进制码、二进制补码、格雷码,格雷码适用于高速转换场景,可减少码值跳变时的误码率。

2. 三大主流 ADC 架构深度解剖:核心原理、数学模型与电路实现

当前工业界超 80% 的市场被 SAR、Σ-Δ 和 Pipeline 三大架构占据,以下从物理层工作机制、数学模型推导、核心电路时序三个维度深度解析其原理,并补充原理层面的瓶颈与优化逻辑。

2.1 逐次逼近型(SAR)ADC —— 电荷重分配的二分法迭代原理

SAR ADC 的核心是“通过迭代缩小输入信号的电压范围”,其原理本质是二进制二分法搜索与电容电荷重分配的结合,无静态功耗的特性源于“仅在转换阶段消耗动态功耗,空闲阶段无电流通路”。

2.1.1 核心原理:逐次逼近的物理过程(以10位SAR为例)

SAR ADC 的转换过程是“位权重逐位判决 + 电荷重分配”的循环,完整步骤如下:

- 采样阶段(Sample Phase):

- CDAC 电容阵列的所有上极板接输入电压 ,下极板接地(全0状态),电容阵列充电至 ,总电荷量 ;

- 采样开关断开后,上极板浮空(电荷守恒),进入判决阶段。

- 逐位判决阶段(Decision Phase):

- 最高位(MSB,第9位)判决:将 CDAC 中权重最大的电容()下极板接参考电压 ,其余仍接地,此时上极板电压为 ;

- 比较器判决 与地电位:若 ,说明 ,保留 MSB 为1;若 ,说明 ,将该电容下极板切回地,MSB 置0;

- 次高位(第8位)判决:对权重为 的电容重复上述操作,此时判决的是“剩余电压范围的二分位”;

- 循环至最低位(LSB),最终 CDAC 下极板的开关状态即为数字输出码。

2.1.2 电荷重分配的数学本质

电荷守恒是 SAR 原理的核心,采样阶段总电荷: 判决阶段,若第 位被置1,对应电容 下极板接 ,总电荷满足: 由电荷守恒 ,推导得: 当所有位判决完成,(量化误差范围内),因此: 其中 为数字输出码(十进制), 为分辨率,这是 SAR ADC 电压-数字转换的核心数学关系。

2.1.3 关键电路模块的原理细节

- 动态锁存比较器:无静态偏置电流,仅在判决瞬间消耗功耗。原理是“正反馈再生”——输入差分电压经预放大级后,送入交叉耦合的反相器对,反相器对的正反馈使微小差分电压迅速放大至电源/地电平,完成判决,判决时间典型值1~10ns;

- 单调电容阵列(Monotonic DAC):传统二进制加权阵列的电容值为 ,单调阵列改为 ,总电容从 降至 ,且开关操作仅需“从MSB到LSB依次置1”,避免二进制阵列的“多次翻转”,降低电荷注入误差。

2.2 Σ-Δ 调制型 ADC —— 过采样+噪声整形的闭环噪声压制原理

Σ-Δ ADC 不追求“单次采样精度”,而是通过“高频过采样”和“闭环噪声整形”将量化噪声推至信号带宽外,再通过数字滤波滤除,核心是闭环负反馈与离散时间域的噪声传递函数设计。

2.2.1 核心原理:1阶Σ-Δ调制器的时域工作机制

1阶Σ-Δ调制器是理解其原理的基础,结构为“积分器 + 1位量化器(比较器) + 1位DAC + 减法器”,闭环工作流程:

- 输入信号与反馈信号相减:减法器输出 ,其中 是1位DAC的输出(仅为 或 );

- 积分器累积误差:积分器对 进行离散时间积分,输出 ( 为采样周期);

- 量化器判决:比较器将 与地比较,输出1位数字码 (1对应 ,0对应 );

- 反馈闭环: 经1位DAC转换为 ,再次送入减法器,形成负反馈。

其核心逻辑是:积分器会“累积输入信号与反馈信号的误差”,迫使反馈信号的平均值逼近输入信号,而量化噪声被积分器“整形”到高频。

2.2.2 噪声整形的数学推导(z域模型)

将Σ-Δ调制器建模为z域线性系统:

- 信号传递函数(STF):输入信号到输出的传递函数,(1阶调制器);

- 噪声传递函数(NTF):量化噪声到输出的传递函数,; 其中 为输入信号z变换, 为输出码流z变换, 为量化噪声z变换。

输出码流的z域表达式为: 将 代入NTF,得频域特性: 可见:

- 低频段(信号带宽内):,量化噪声被压制;

- 高频段: 随频率增大而增大,量化噪声被推至高频(噪声整形)。

2.2.3 过采样率与信噪比的定量关系

过采样率 ( 为信号带宽),量化噪声的总功率为 ,经噪声整形后,带内噪声功率为: 其中 为调制器阶数,由此推导信噪比(SNR)提升公式: 以2阶调制器()、OSR=256为例: 这意味着即使1位量化器(理论SNR≈6dB),经2阶调制+OSR=256后,SNR可提升至126dB,等效20位以上分辨率。

2.2.4 多比特Σ-Δ的核心改进原理

1阶1比特Σ-Δ存在“空闲音”和低SNR问题,多比特Σ-Δ将量化器扩展为M位(M=3~5),核心改进:

- 量化台阶从 降至 ,量化噪声功率降低 倍;

- 引入动态元件匹配(DEM):将多比特DAC的电容/电阻单元随机化选择,原理是“将元件失配的确定性误差转换为随机噪声”,例如数据加权平均(DWA)算法,按输出码的权重循环选择DAC单元,使失配误差的功率谱均匀分布在整个采样带宽,带内误差被大幅压制。

2.3 流水线型(Pipeline)ADC —— 多级级联的残差放大与数字校正原理

Pipeline ADC 的核心原理是“分阶段量化 + 残差传递”,将N位的量化任务拆解为K级(通常K=N/1.5),每级仅量化1.5位,剩余“残差电压”经放大后传递至下一级,最终通过数字校正合并所有级的输出,实现高精度量化。

2.3.1 核心原理:1.5位单级Pipeline的完整工作流程

1.5位是Pipeline最经典的单级设计,其量化范围为 ,判决阈值为 ,完整工作分为4个阶段:

- 采样阶段:SHA采样输入电压 ,并将其传递至子ADC和MDAC;

- 子ADC量化:1.5位Flash子ADC对 判决,输出2位数字码(),对应4种状态:

- :;

- :;

- :;

- 残差生成:1.5位DAC根据子ADC输出,生成补偿电压 (),MDAC的减法器计算残差电压 ;

- 残差放大与传递:MDAC的运放将 放大2倍(固定增益),输出 ,传递至下一级作为输入。

2.3.2 数字校正的核心数学原理

单级1.5位的量化存在“冗余位”,这是数字校正的基础。以12位Pipeline(8级1.5位)为例,每级输出2位,总输出16位,其中4位为冗余位,数字校正的核心是:

- 每级的残差放大增益为2,因此第k级的输出对最终结果的权重为 ;

- 数字校正逻辑将所有级的输出按权重叠加,并消除冗余位,最终输出12位有效码: 其中 为第k级的2位输出, 为冗余位补偿值。

冗余位的关键作用是:允许单级的量化误差(如比较器失调)被下一级“覆盖”,无需高精度模拟电路,仅需数字逻辑即可校正,这是Pipeline ADC 兼顾速度与精度的核心。

2.3.3 MDAC的核心电路原理

MDAC(Multiplying DAC)是Pipeline的核心模块,兼具“数模转换”“减法”“放大”三大功能,原理如下:

- 电路结构:由采样电容、反馈电容、运算放大器组成的开关电容电路;

- 采样阶段:采样电容充电至输入电压 ,反馈电容放电至0;

- 放大阶段:采样电容与反馈电容串联,运放工作在负反馈状态,闭环增益由电容比值决定(),典型增益为2;

- 乘法特性:增益随反馈电容的电压(DAC输出)变化,因此称为“乘性DAC”,其线性度直接决定Pipeline的INL/DNL。

2.4 三大主流架构综合对比列表

为了在工程选型中提供直观参考,特将三大主流架构的核心参数进行横向列表对比(补充关键工程维度):

| 维度 / 架构 | SAR ADC | Σ-Δ 调制型 ADC | 流水线型 (Pipeline) ADC |

|---|---|---|---|

| 工作原理核心 | 逐次逼近二分法,电荷重分配 | 过采样,噪声整形,数字滤波抽取 | 空间展开,多级流水作业,MDAC放大残差 |

| 核心原理本质 | 开环电荷重分配 + 二进制二分法搜索 | 闭环负反馈 + 过采样 + 噪声整形 | 多级开环量化 + 残差放大 + 数字校正 |

| 典型分辨率 | 8 ~ 18 bits | 16 ~ 32 bits(有效位24~28bit) | 8 ~ 16 bits |

| 典型采样率 | 100 kSPS ~ 10 MSPS(交织架构可达100 MSPS) | 几 SPS ~ 数 MHz (有效带宽,OSR=64~256) | 50 MSPS ~ 5 GSPS(8位Flash+Pipeline可达10 GSPS) |

| 速度限制原理 | 逐位判决的串行操作(N次判决) | 数字抽取滤波器的组建立时间 | 运放的建立时间(带宽限制) |

| 功耗水平 | 极低 (W ~ mW 级),动态主导 | 中等 (mW 级,数字滤波占功耗40%) | 高 (mW ~ W 级),静态主导(运放偏置占70%) |

| 延迟特性 (Latency) | 零延迟(转换完成即输出),适合多路复用 | 长延迟(ms级,由抽取滤波器决定) | 中等延迟(数十个时钟周期,级数×单级延迟) |

| 前端抗混叠滤波要求 | 严格 (陡峭阶数,8~10阶有源滤波器) | 极度宽松 (1~2阶RC滤波器即可) | 严格 (6~8阶有源滤波器,需匹配信号带宽) |

| 主要性能瓶颈 | 电容匹配精度(<0.1%)、反冲电荷 (Kickback)、交织通道失配 | 时钟抖动(<10ps rms)、带外噪声、空闲音 | MDAC增益带宽积 (GBW)、级间失配、功耗 |

| 量化误差来源 | 电容匹配误差 + 电荷注入误差 | 量化器分辨率 + 时钟抖动 | 运放有限增益 + 级间失配 + 比较器失调 |

| 关键数学模型 | 电荷守恒 + 二进制权重分配 | z域噪声传递函数 (NTF) + 过采样率 | 残差放大增益 + 数字权重叠加 |

| 反馈机制 | 无反馈,纯开环判决 | 强闭环负反馈(压制信号噪声) | 单级局部反馈(MDAC),整体开环 |

| 精度实现方式 | 提升电容匹配精度(<0.1%) | 提升过采样率 + 调制器阶数 | 数字校正补偿模拟误差 |

| 品质因数 (FoM) | 5~10 fJ/conv-step(7nm工艺) | 10~50 fJ/conv-step(数字滤波占比高) | 50~200 fJ/conv-step(高速架构>200) |

| 工艺适配性 | 适配先进工艺(7~28nm FinFET),面积小 | 适配成熟工艺(40~180nm),数字占比高 | 适配中节点工艺(28~65nm),模拟占比高 |

| 成本 | 极低(无源电容+数字逻辑,无高精度运放) | 中等(数字滤波器占芯片面积50%) | 高(多通道运放+高速比较器,掩膜成本高) |

| 抗EMI能力 | 中等(电容阵列易受电磁干扰) | 高(过采样+噪声整形抑制干扰) | 低(高速模拟电路对EMI敏感) |

| 校准需求 | 低(出厂一次性校准,无需后台校准) | 中(部分架构需DEM,无后台校准) | 高(必须后台校准补偿级间误差) |

| 典型应用场景 | DAQ系统、电机闭环控制、IoT传感器、消费电子 | 电子秤、精密仪器、高保真音频、医疗监测 | 5G通信基站基带、相控阵雷达、高端示波器 |

3. 特种与前沿 ADC 拓扑博览(少见但极具专业性)

在主流架构之外,为了应对极限速度、极限面积、或极其特殊的数字工艺节点挑战,学术界与工业界演化出了众多专精特尖的 ADC 拓扑。以下盘点 8 种具有高度专业代表性的特种架构:

- 闪速型全并行 (Flash) ADC

- 核心机制:并行极致的速度极限。利用 个精密电阻构成的分压网络和对应数量的高速锁存比较器,对输入信号进行“一锤定音”的并行比较,直接生成温度计码,随后经逻辑电路转码为二进制。

- 架构特点:速度极快(皮秒级响应,轻松突破 10 GSPS),零流水线延迟;但比较器数量与输入寄生电容随分辨率指数爆炸,极其消耗功耗并严重拖垮前端驱动放大器。

- 典型应用:超高速光通信接收端、示波器测量核心(通常局限于 6~8 位低分辨率场景)。

- 折叠插值型 (Folding & Interpolation) ADC

- 核心机制:Flash 架构的面积与功耗救星。前端采用模拟差分折叠电路,将宽泛的输入电压范围“折叠”成几个重复的窄区间,后接电阻插值网络生成密集的参考阈值,大幅复用下游比较器。

- 架构特点:将比较器数量从 剧减至十分之一甚至更低,在维持极高采样率的同时,显著优化了功耗与前端输入电容负荷。

- 典型应用:宽带中频雷达接收机、高速数字视频广播(DVB)。

- 两步式 / 分段式 (Two-Step / Subranging) ADC

- 核心机制:流水线架构的极简版。放弃深度的流水线级联,仅分两级转换。第一级 Flash 完成粗量化(Coarse),经由 DAC 转回模拟量与输入求差,残差放大后送入第二级 Flash 进行细量化(Fine)。

- 架构特点:规避了深流水线架构长达十几个时钟周期的长延迟,同时将硬件面积控制在适中水平。

- 典型应用:图像传感器 (CIS) 的高速列级 ADC、对延迟极度敏感的高速数字控制系统。

- 双斜率积分型 (Dual-Slope Integrating) ADC

- 核心机制:利用高精度积分器先对输入待测电压进行固定时间 () 的正向积分,随后切换至极性相反的精密参考电压进行反向积分直至输出过零,通过内部计数器测量反向积分时间 ()。根据等式 计算最终结果。

- 架构特点:转换速率极慢(几十 SPS),但其固定时间积分特性使其对高频白噪声,特别是对固定周期的工频(50/60Hz 及其整数倍谐波)串扰,具有理论上无限的共模与周期性串扰抑制能力(极深的频域陷波特性)。

- 典型应用:高精度数字万用表(DMM,精度可达 6.5 位至 8.5 位)、高稳定性精密仪器面板表。

- 压控振荡器型 (VCO-based) ADC

- 核心机制:将输入模拟电压作为控制电压,注入环形压控振荡器(VCO),将其转换为时域的频率或相位变化,随后利用数字相位计数器或鉴相器(TDC)对其进行纯数字量化。

- 架构特点:相位作为频率的积分,使得该架构天生具备一阶噪声整形能力。因其硬件实现几乎全部由纯数字逻辑门(如反相器延迟链)构成,摒弃了高增益运放,在电压裕度极低的 5nm/3nm 等先进纯数字 CMOS 工艺中如鱼得水,是当前国际固态电路会议(ISSCC)最为瞩目的前沿架构之一。

- 时间编码型 (Time-Encoded / TDC-based) ADC

- 核心机制:数据域的二次映射:电压 时间 数字。前端利用电压控制延迟线 (VCDL) 将模拟幅度的高低映射为脉冲跳变沿的绝对延迟时间差,后端利用皮秒级的时间数字转换器 (TDC) 测量该时间间隔。

- 架构特点:巧妙利用先进半导体工艺节点中极高的时间分辨率(门延迟 Gate Delay 可低至几皮秒)来规避且替代已严重恶化的电压幅度分辨率,实现高精度量化。

- 典型应用:太赫兹超宽带通信接收机、先进工艺节点下的极限射频直采系统。

- 循环型 / 算法型 (Cyclic / Algorithmic) ADC

- 核心机制:折叠在时间维度上的 Pipeline。物理电路上仅存在“一个”完整的流水线级(包含子 ADC、DAC、减法器与残差放大器),通过引入反馈开关环路,使得残差信号在时间轴上循环通过该单一物理模块 N 次,从而提取出 N 位的分辨率。

- 架构特点:将硅片版图面积压缩到了极致的物理下限,付出的代价是极大地牺牲了吞吐量,必须耗费 N 个完整的时钟周期才能输出一次最终结果。

- 典型应用:面积受限极其严苛的微型化植入式医疗传感器、高密度百万像素级 CMOS 图像传感器(CIS)阵列的像素级量化单元。

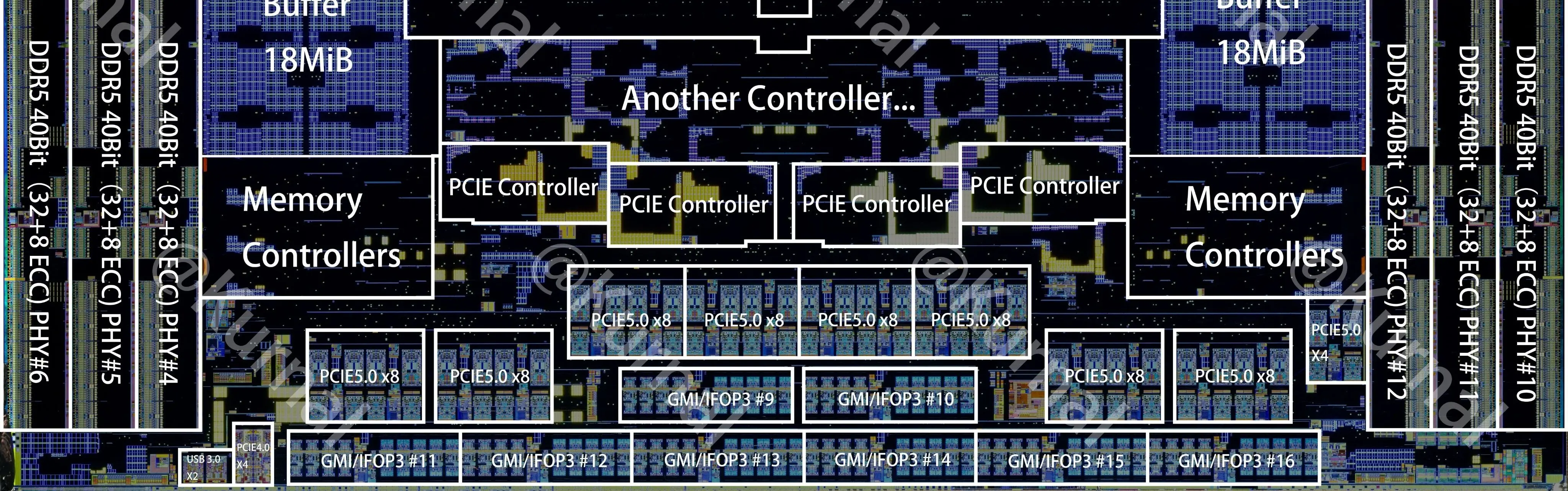

- 时间交织 (Time-Interleaved, TI) ADC

- 核心机制:TI 并非一种底层的单核量化机制,而是一种宏观的系统级拓扑阵列。将 M 个完全相同的单核子 ADC(如 SAR 或 Pipeline)高度并联,由一组相位彼此精确相差 的多相时钟网络交替触发各个子核心依次进行采样与转换。

- 架构特点:系统宏观总采样率直接等比例跃升 M 倍,是目前突破几十乃至上百 GSPS 超高采样率壁垒的唯一终极方案。

- 瓶颈与挑战:面临极其严峻的通道间模拟物理失配(包括静态失调 Offset、满量程增益 Gain,特别是高频信号下最为致命的时序偏斜 Timing Skew)。微小的失配即会在输出频谱中引发大量的交织杂散(Interleaving Spurs,俗称“交织鬼影”),系统必须付出巨大的硅片面积代价,依赖极为复杂的自适应全数字后台滤波器(DSP)进行盲校准与抵消。

4. 场景映射与系统级 PCB 信号完整性工程指南

在严苛的硬件工程实践中,半导体厂商规格书(Datasheet)首页标称的指标仅代表极其理想实验室环境下的性能上限。若缺乏扎实的板级信号完整性(SI)和电源完整性(PI)设计底蕴,ADC 在实际系统中的动态性能往往会遭遇“断崖式”降级。

4.1 工业高精度采集的工程挑战:反冲电荷 (Kickback)

- 物理现象:在多通道 SAR ADC 切换输入多路复用器并闭合内部采样开关的极短瞬间,由于 CDAC 在上一次转换结束时累积的残余电荷未能清零,这些电荷会剧烈地倒灌回外部输入源,产生极陡峭且幅度巨大的瞬态电流尖峰。若前端驱动器闭环带宽不够或阶跃响应建立时间过长,将导致采样节点的电压在极短的采样捕获窗口(Acquisition Time)结束前无法稳定至理想值,从而引发极其严重的谐波失真与串扰。

- 系统级对策:绝不可将高阻抗输出的传感器(如裸分压电阻网络)直接连接至 ADC 模拟引脚。必须在 ADC 模拟输入前端紧密部署具有极高增益带宽积(GBW)和极快压摆率的全差分放大器 (FDA)。更关键的是,在 FDA 运放输出端与 ADC 输入引脚之间,必须精准设计并调试 电荷桶吸收滤波器 (Charge Bucket Filter)。其中的 需选取电容值至少为 ADC 内部采样电容 20~50 倍的极低介质吸收与压电效应的陶瓷电容(强制要求 C0G/NP0 材质),使其充当吸收瞬态反冲电流的“电荷蓄水池(Charge Reservoir)”。

4.2 高速系统信噪比的刚性天花板:时钟网络抖动

- 物理现象:在射频直采架构中(例如面对 1GHz 的中频输入载波),采样时钟边沿哪怕仅发生几百飞秒(秒)的微小时间晃动,也会将高频信号自身极高的压摆率(Slew Rate, )按照微分关系,直接转化为极其庞大的幅度采样误差,这将无情地拉高系统整个奈奎斯特带宽内的宽带本底噪声,彻底摧毁 SNR。

- 系统级对策:对于工作在 GSPS 级别的高速 Pipeline 或 TI-ADC 阵列,严禁图省事使用 FPGA 内部自带的常规 PLL 或廉价普通石英晶振直接驱动 ADC 的主采样时钟引脚。硬件架构上必须引入外部专用的超低相位噪声时钟发生器及抖动清除器(Jitter Cleaner,例如 LMK04828 / HMC7044 级别),确保整个时钟分配网络的宽带 RMS 抖动被严密压制在 <100fs 以内。在 PCB 布线层面,时钟网络强制使用阻抗严格受控的差分微带线或内层带状线(推荐 LVPECL / LVDS / CML 电平标准),正负端必须实现极其苛刻的物理等长,且在时钟走线两侧的净空区域敷设高密度的接地过孔(Ground Vias),构筑类似“同轴电缆”的法拉第屏蔽效应,坚决杜绝任何相邻高频数据线的电磁串扰。

4.3 动态基准电源 (VREF) 与全频带目标阻抗 (Target Impedance)

- 物理现象:高分辨率(>16-bit)的 SAR 或 Σ-Δ ADC 在执行逐次逼近转换期间,其内部庞大的电容开关阵列会以极高的开关频率(通常数十 MHz)从 VREF 外部引脚急剧抽吸突变的瞬态脉冲电流。若基准供电网络(PDN)的物理路径存在哪怕几个纳亨(nH)的微小寄生电感(ESL),根据法拉第定律 ,基准端将发生严重的瞬态电压跌落(Voltage Droop),这会直接且不可逆地毁掉每一次转换判决的精准度,恶化 DNL 和 INL。

- 系统级对策:彻底摒弃使用普通低带宽慢速 LDO 直接为高精度 ADC 基准端供电的侥幸心理。强制在系统架构中引入高频瞬态电流供给能力极佳的专用宽带基准缓冲器(Reference Buffer,如 OPA350 级别的精密运放),并在 PCB 物理布局上,将其置于离 ADC 的 REF 引脚**“零物理距离”**的位置。同时,在 REF 引脚处必须严格采用容值跨度多达几个数量级的多电容并联退耦策略(例如,10μF 大容量 X5R/X7R 提供低频能量 + 0.1μF C0G 应对中频 + 1000pF 超低 ESL 极小封装电容滤除高频),通过精确的谐振点错位,为 VREF 节点构筑一个从直流到数百 MHz 的全频带极低目标阻抗(Target Impedance)的低阻能量池。

4.4 混合信号接地与回流拓扑哲学

- 系统级对策:过去十年间工业界广泛流传的“将模拟地(AGND)与数字地(DGND)在 PCB 内层实行物理割裂(Split Ground),随后仅在 ADC 芯片正下方通过单颗磁珠或 0 欧姆电阻进行单点连接”的陈旧理念,在当今高频、宽带、密集的混合信号系统中已被大量的 EMI/EMC 翻车案例证实为设计灾难,它极易切断高频回流路径,导致地平面间产生强烈的偶极子天线辐射效应。当前微波射频与高速混合信号设计的最高权威实践是:强烈建议采用一整块完整、连续且坚如磐石的统一地平面(Solid Ground Plane)。硬件工程师应将全部精力倾注于元器件布局与信号走线的严密宏观物理分区 (Placement and Routing Partitioning) 上。具体而言,将所有极度敏感的纯模拟前端电路(传感器、FDA、基准缓冲器)严格约束在 PCB 的一侧,将所有高噪声数字处理器(FPGA、DSP、DDR 内存)及高频开关电源(SMPS)驱逐至物理隔离的另一侧。核心原则是:利用高频电磁场理论中“高频电流总是严格沿着最小电感路径(即信号走线的正下方地平面投影)回流(Return Current)”的物理天性,从宏观拓扑上确保汹涌的数字高频返回电流的物理最短路径绝对不会、也不需要横穿那片宁静且脆弱的模拟前端处女地。

5. 站在硅片之巅:ADC 技术的未来发展趋势展望

随着摩尔定律的艰难推进与新兴应用场景的井喷,ADC 架构正迎来前所未有的深刻变革。未来的 ADC 将不仅仅是一个被动的“转换器”,而将成为智能系统感知物理世界的“主动引擎”。

5.1 架构融合与“数字定义模拟” (Digital-Defined Analog)

单一架构的物理红利已触及天花板,未来的顶尖 ADC 将无一例外地走向混合架构 (Hybrid Architectures)。

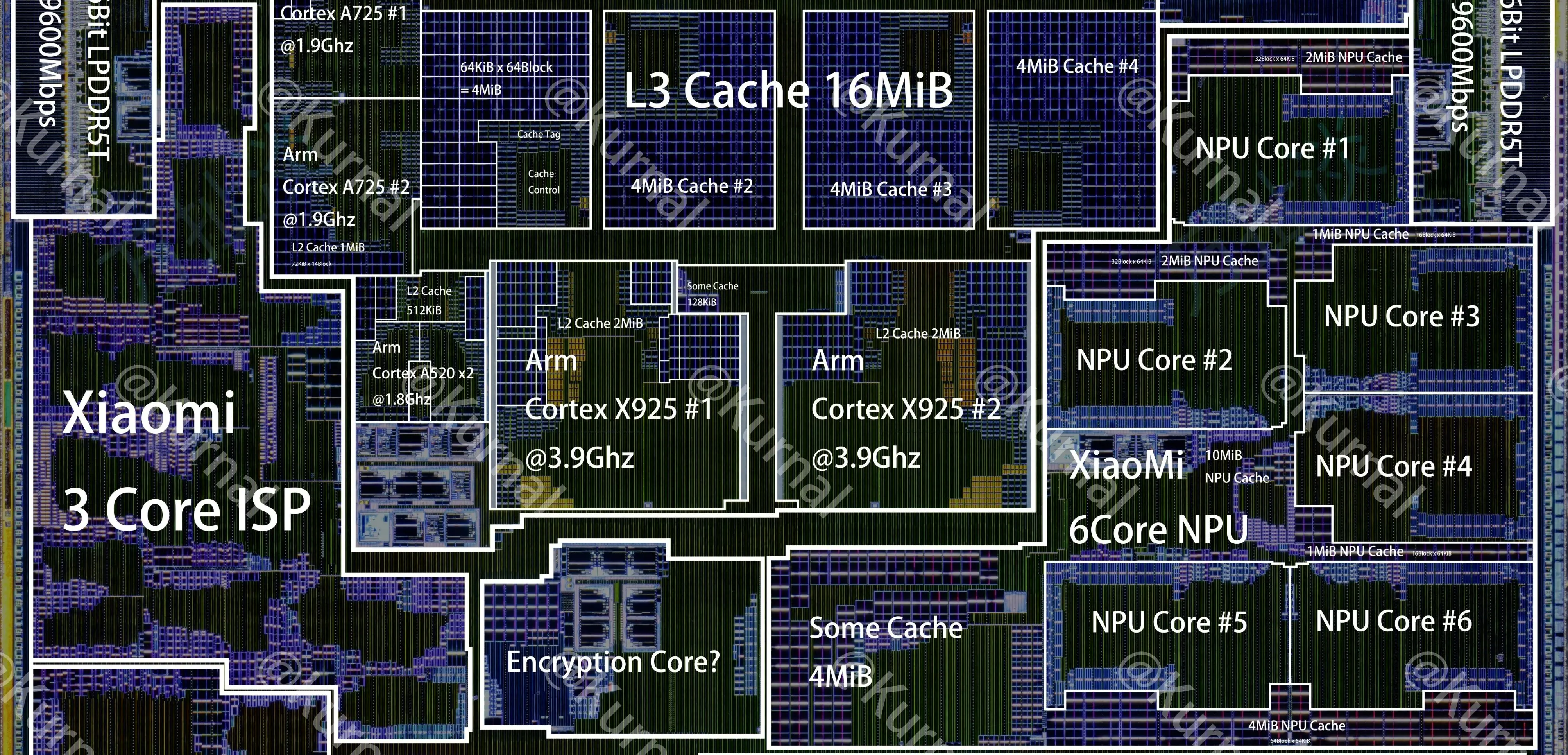

- 噪声整形 SAR (NS-SAR):将 Σ-Δ 的高精度(噪声整形)与 SAR 的极低功耗完美结合,用极小的面积实现了 14-bit 以上的中速高能效转换,正统治低功耗 IoT 与音频节点。

- Pipelined-SAR:前级采用低精度 Pipeline 处理高速残差,后级利用 SAR 解决高精度量化,兼具两者的速度与能效。

- 数字后台校准的全面接管:随着 3nm/2nm 先进工艺下模拟电压裕度几乎消失,高增益运放将彻底退出历史舞台。取而代之的是纯数字逻辑门(如 VCO-based 架构)和庞大的 AI 加持数字预失真/后台校准引擎。“用晶体管数量换取模拟精度”将成为不可逆转的趋势。

5.2 极大规模时间交织 (Massive TI) 与智能校准

面向 6G 毫米波、太赫兹通信以及 800G 光收发器(DSP-based Optical Transceivers),单通道 ADC 的速度极限(约 10 GSPS)已远远不够。

- 未来的系统将采用 64、128 甚至 256 通道的极大规模时间交织 (Massive TI-ADC) 技术,实现 >100 GSPS 的恐怖采样率。

- 面对成百上千个通道间极其复杂的温度、电压与老化漂移,传统的确定性校准算法已无能为力。基于机器学习(ML)与神经网络的盲自适应校准算法将被直接固化入 ADC 芯片内部的数字内核中,实现对时序偏斜(Timing Skew)和非线性失真的“无感”实时补偿。

5.3 边缘计算与传感-计算一体化 (Compute-in-Memory)

在万物互联与 TinyML 的驱动下,ADC 将与传感器前端及神经网络加速器深度融合。

- 事件驱动型 (Event-Driven) ADC:告别持续采样的高功耗模式,ADC 仅在输入信号发生显著跳变(如声音唤醒、心率异常)时才启动高精度转换,休眠功耗降至皮瓦(pW)级。

- 存算一体化 (CIM):ADC 不再仅仅输出原始的电压数字码,而是直接在模拟域或数模混合域完成特征提取(如乘加运算 MAC)。传感器捕获的数据经过 ADC 转换后,直接输出的已经是“语音识别结果”或“图像特征向量”,从而极大降低了数据搬运的功耗延迟。

5.4 极端物理环境下的探索 (Cryogenic & Space)

随着量子计算与深空探测的崛起,ADC 必须学会在极端的物理边界下生存。

- 深低温 (Cryogenic) ADC:量子计算机的超导量子位必须工作在极低温度(4 Kelvin 甚至几十 mK)。将 ADC 从常温区移入极低温恒温器内部,可极大地减少长线缆带来的热噪声和干扰。这类 ADC 必须在保持数 GSPS 速度的同时,将功耗压榨至极低水平(几毫瓦),以防止自身发热导致超导环境崩溃。

附录 ADC术语解释以及公式计算

一、术语解释

1. 基础特性类

| 术语缩写 | 英文全称 | 中文名称 | 核心解释(含单位) |

|---|---|---|---|

| ADC | Analog-to-Digital Converter | 模数转换器 | 将连续模拟电压/电流信号转换为离散数字码的核心器件,是数模系统的桥梁;无固定单位。 |

| Resolution | - | 分辨率 | ADC的标称位数,表征对模拟信号的细分能力,位数越高可分辨的电压变化越小;单位:bit(位)(常见8/12/16/24 bit)。 |

| FSR | Full Scale Range | 满量程范围 | ADC能正确转换的模拟输入电压/电流的极值范围;单位:V(伏特)/mA(毫安)(如单极性0 |

| VLSB | Voltage per Least Significant Bit | 每LSB电压值 | 1个最低有效位对应的模拟电压量(量化台阶),是分辨率的物理体现;单位:V(伏特)/mV(毫伏)/μV(微伏)。 |

| LSB | Least Significant Bit | 最低有效位 | 数字输出码中权重最小的位,对应,是ADC的最小量化单位;无固定单位(常作为误差类指标的计量基准)。 |

| MSB | Most Significant Bit | 最高有效位 | 数字输出码中权重最大的位,对应FSR的1/2,决定输入信号的量级范围;无固定单位。 |

| Conversion Time | - | 转换时间 | ADC完成一次“模拟输入→数字输出”的总耗时(含采样、量化、编码);单位:ns(纳秒)/μs(微秒)/ms(毫秒),与采样率成反比。 |

| Throughput | - | 吞吐率 | 单位时间内ADC可完成的有效转换次数;单位:SPS(Samples Per Second,采样次数/秒)(如1kSPS、1MSPS),通常等于采样率(架构受限场景下可更低)。 |

| Input Impedance | - | 输入阻抗 | ADC模拟输入端对外部信号源的等效阻抗,高输入阻抗可减少对信号源的负载影响;单位:Ω(欧姆)/MΩ(兆欧)(理想值趋近无穷大)。 |

| Input Range | - | 输入范围 | 实际可接入的模拟输入信号范围(可略大于FSR,超量程时输出会钳位或溢出);单位:V(伏特)。 |

2. 误差与失真类

| 术语缩写 | 英文全称 | 中文名称 | 核心解释(含单位) |

|---|---|---|---|

| Quantization Error | - | 量化误差 | 模拟信号量化为数字码时的固有误差(因“取整”导致),峰值为,又称量化噪声;单位:V(伏特)/LSB(最低有效位)。 |

| Offset Error | - | 失调误差 | 零输入模拟信号时,ADC输出数字码偏离理想值对应的电压偏差;单位:LSB(最低有效位)/mV(毫伏)/μV(微伏),可通过校准消除。 |

| Gain Error | - | 增益误差 | ADC实际转换曲线的斜率与理想斜率的偏差,反映满量程输出的整体偏差;单位:%FSR(满量程百分比)/LSB(最低有效位)。 |

| INL | Integral Nonlinearity | 积分非线性 | 实际转换曲线与理想直线的最大累积偏差,反映整体线性度,超标会导致“码丢失”;单位:LSB(最低有效位)(常见指标≤±1 LSB)。 |

| DNL | Differential Nonlinearity | 微分非线性 | 相邻数字码对应的实际电压步长与理想的偏差;单位:LSB(最低有效位);DNL>1会导致码丢失,DNL<0会导致码重复。 |

| THD | Total Harmonic Distortion | 总谐波失真 | 输出信号中所有谐波分量的总功率与基波功率的比值,反映ADC的非线性失真程度;单位:%(百分比)/dB(分贝)(工程常用-60dB~-120dB)。 |

| THD+N | Total Harmonic Distortion plus Noise | 总谐波失真加噪声 | THD与量化噪声、热噪声等所有噪声分量的总和,更贴近实际应用场景的失真评估指标;单位:%(百分比)/dB(分贝)。 |

| SFDR | Spurious Free Dynamic Range | 无杂散动态范围 | 基波信号功率与最大杂散信号功率的比值,反映ADC抑制非谐波杂散的能力;单位:dB(分贝)(高性能ADC可达100dB以上)。 |

| Harmonic Distortion | - | 谐波失真 | 输入纯正弦波时,输出信号中除基波外的整数倍频率分量(如2次、3次谐波),是非线性的直接体现;单位:dBc(相对于基波的分贝数)。 |

| Aliasing | - | 混叠失真 | 采样率低于奈奎斯特频率时,高频信号被错误折叠到低频段的失真,无法通过后期处理恢复;无固定单位。 |

| Glitch | - | 毛刺 | 转换过程中输出数字码出现的短暂错误跳变(通常由电源波动、电磁干扰导致),影响数据稳定性;单位:ns(纳秒,持续时间)/LSB(幅值偏差)。 |

3. 性能指标类

| 术语缩写 | 英文全称 | 中文名称 | 核心解释(含单位) |

|---|---|---|---|

| SNR | Signal-to-Noise Ratio | 信噪比 | 有用信号功率与噪声功率的比值(不含谐波),值越高信号还原度越好;单位:dB(分贝)(理想12位ADC约74dB)。 |

| ENOB | Effective Number of Bits | 有效位数 | 考虑噪声、失真后的实际有效分辨率,公式为,是ADC实际性能的核心衡量指标;单位:bit(位)。 |

| DNR | Dynamic Range | 动态范围 | ADC能正确检测的最大信号与最小可分辨信号的功率比,反映对强弱信号的兼容能力;单位:dB(分贝)。 |

| PSRR | Power Supply Rejection Ratio | 电源抑制比 | 电源电压变化引起的输出误差与电源变化量的比值,值越高抗电源波动能力越强;单位:dB(分贝)(常见≥60dB)。 |

| CMRR | Common Mode Rejection Ratio | 共模抑制比 | 对输入信号中共模分量(如地线干扰)的抑制能力,差分ADC核心指标;单位:dB(分贝)(理想值∞,工业级≥80dB)。 |

| BER | Bit Error Rate | 误码率 | 输出数字码中错误位的占比,反映ADC数据传输/转换的可靠性;无量纲(工业级要求通常<10⁻⁹)。 |

| TOI | Third-Order Intercept Point | 三阶交调点 | 衡量ADC抗互调失真的能力,值越高多信号输入时的非线性失真越小;单位:dBm(分贝毫瓦)。 |

| Noise Floor | - | 噪声底 | ADC无信号输入时的固有噪声功率水平,决定最小可检测信号的下限;单位:dBV/√Hz(分贝伏/根号赫兹)/nV/√Hz(纳伏/根号赫兹)。 |

4. 采样/架构类

| 术语缩写 | 英文全称 | 中文名称 | 核心解释(含单位) |

|---|---|---|---|

| fs | Sampling Rate | 采样率 | 单位时间内对模拟信号的采样次数;单位:SPS(Samples Per Second)/Hz(赫兹)(如1kSPS=1kHz、1MSPS=1MHz、1GSPS=1GHz)。 |

| Nyquist Frequency | - | 奈奎斯特频率 | 采样率的一半(fs/2),是避免混叠的临界频率,输入信号最高频率需低于该值;单位:Hz(赫兹)。 |

| Anti-Aliasing Filter | - | 抗混叠滤波器 | 采样前的低通滤波器,滤除高于奈奎斯特频率的信号分量,防止混叠失真;核心参数单位:Hz(截止频率)/dB(衰减量)。 |

| S/H | Sample-and-Hold | 采样保持电路 | ADC核心子模块,在采样阶段捕捉模拟信号,保持阶段稳定信号以便量化,决定采样精度;核心参数单位:ns(捕捉时间)/V(保持电压精度)。 |

| SAR | Successive Approximation Register | 逐次逼近型ADC | 主流中速ADC架构(12 |

| ΔΣ | Delta-Sigma (Sigma-Delta) | 三角积分型ADC | 高精度低速ADC架构(16~24位,<1MSPS),通过过采样+噪声整形提升分辨率,适用于工业测量;无固定单位。 |

| Pipeline | - | 流水线型ADC | 高速高精度ADC架构(8 |

| Flash | - | 闪存型(并行)ADC | 超高速ADC架构(≤8位,>1GSPS),通过电阻分压+比较器直接量化,速度最快但功耗、成本高;无固定单位。 |

| OSR | Oversampling Rate | 过采样率 | 实际采样率与信号带宽的比值(ΔΣ ADC核心参数),OSR越高噪声整形效果越好,分辨率越高;无量纲(常见64/128/256倍)。 |

5. 接口/校准类

| 术语缩写 | 英文全称 | 中文名称 | 核心解释(含单位) |

|---|---|---|---|

| SPI | Serial Peripheral Interface | 串行外设接口 | 主流ADC数字接口(三线/四线),低速、低引脚数,适用于SAR/ΔΣ ADC;单位:bps(比特率)/MHz(时钟频率)(常见≤50MHz)。 |

| I2C | Inter-Integrated Circuit | 集成电路总线 | 两线式串行接口,支持多设备挂载,适用于低速率、小批量数据传输;单位:bps(比特率)(标准模式100kbps,快速模式400kbps)。 |

| LVDS | Low Voltage Differential Signaling | 低压差分信号 | 高速ADC接口,抗干扰能力强,传输速率可达Gbps级,适用于Pipeline/Flash ADC;单位:Gbps(吉比特/秒)/V(摆幅,典型0.35V)。 |

| Parallel Interface | - | 并行接口 | 多引脚并行输出数字码,速度快但引脚多,适用于超高速Flash ADC;单位:MHz(时钟频率)/Mbps(传输速率)。 |

| JESD204B/C | - | 高速串行接口标准 | 面向高速ADC/DAC的串行接口协议,支持多通道、高带宽,适用于通信领域;单位:Gbps(每通道速率,典型12.5Gbps)。 |

| Self-Calibration | - | 自校准 | ADC内置的校准算法,自动消除失调、增益、INL/DNL误差;单位:ms(校准耗时)(典型1~10ms)。 |

| Offset Calibration | - | 失调校准 | 单独校准零输入时的输出偏差,分为硬件校准(调电位器)、软件校准(数字补偿);校准精度单位:μV(微伏)/LSB(最低有效位)。 |

| Gain Calibration | - | 增益校准 | 校准满量程输入时的输出偏差,通过调整内部放大器增益或数字增益系数实现;校准精度单位:%FSR(满量程百分比)/LSB(最低有效位)。 |

| System Calibration | - | 系统级校准 | 包含ADC、前端放大器、滤波器的整体校准,消除系统级误差,提升整体精度;校准精度单位:ppm(百万分比)/LSB(最低有效位)。 |

二公式计算

1. 基础量化相关

(1)量化台阶(VLSB)

- 变量说明:

- :量化台阶(单位:V);

- :ADC的满量程输入电压范围(单位:V);

- :ADC的标称分辨率(单位:bit);

- 近似条件:当时,,误差可忽略。

(2)量化误差(峰值/均方根)

- 变量说明:

- :量化误差峰值(单位:V);

- :量化误差均方根值(单位:V);

- 说明:理想ADC的量化误差峰值为半个量化台阶,是ADC的固有误差,无法完全消除。

2. 采样与抗混叠

(1)奈奎斯特采样定理

- 变量说明:

- :采样率(单位:Hz);

- :模拟输入信号的最高频率(单位:Hz);

- 说明:若不满足该条件,会出现混叠失真,导致数字信号无法还原原始模拟信号。

(2)过采样率(OSR)与分辨率提升

- 变量说明:

- :分辨率提升量(单位:bit);

- :过采样率(无单位);

- :提升后的有效分辨率(单位:bit);

- :标称分辨率(单位:bit);

- 说明:ΔΣ ADC中,OSR每提升4倍,有效分辨率约增加1位。

3. 性能指标计算

(1)理想SNR(无失真)

- 变量说明:

- :理想信噪比(单位:dB);

- :ADC的标称分辨率(单位:bit);

- 修正:双极性信号需额外加0.17dB,即(单位:dB)。

(2)有效位数(ENOB)

- 变量说明:

- :有效位数(单位:bit);

- :实际测量得到的ADC信噪比(单位:dB);

- 扩展:含失真场景(THD+N)下,使用(SNDR为信纳比,单位:dB)。

(3)总谐波失真(THD)

- 变量说明:

- :总谐波失真(单位:dB);

- :基波功率(单位:W/ mW);

- :2/3次谐波功率(单位:W/ mW);

- n取≤10次谐波(工程常用)。

(4)共模抑制比(CMRR)

- 变量说明:

- :共模抑制比(单位:dB);

- :输入共模电压(单位:V);

- :共模电压导致的输出偏差(单位:V)。

4. 误差修正类

(1)失调误差修正

- 变量说明:

- :校准后电压值(单位:V);

- :ADC原始输出值(单位:V);

- :零输入时的实测输出值(单位:V)。

(2)增益误差修正

- 变量说明:

- :理想满量程电压(单位:V);

- :满量程输入时的实测输出值(单位:V)。

5 物理极限与热噪声推导

在所有电路设计中,电阻和晶体管均会产生热噪声。对于采样保持电路中的采样电容 ,其产生的热噪声(也称 噪声)设定了 ADC 物理分辨率的绝对底线。

- 热噪声功率积分公式: (其中 为玻尔兹曼常数 , 为绝对温度,开尔文)

- 工程意义:若要设计高精度(如 20-bit)ADC,总采样电容必须足够大,以使 的电压波动远小于 1 LSB 的幅度。这也是高精度 ADC 功耗和面积无法无限缩小的物理壁垒。

6 理想量化噪声与 SNR 极限公式

- 理想量化噪声均方根 (RMS): 假设量化误差 在 内均匀分布(概率密度函数为 ),其噪声方差(功率)积分推导为:

- 理想信噪比 (Ideal SNR): 对于满量程的正弦波输入(振幅为 ,有效值为 ),系统仅含量化噪声时的理论 SNR 极限:

7 时钟孔径抖动 (Aperture Jitter) 限制推导

当时钟边沿产生时间抖动 (RMS值)时,作用于频率为 的满量程正弦波 上,产生的最大电压误差为 。由此推导出的抖动 SNR 上限:

- 举例:对于 1GHz 的中频输入,若要求系统受时钟抖动限制的 SNR 不低于 60dB,计算得出时钟抖动 必须严格控制在 159 飞秒 (fs) 以内。

8 过采样 (Oversampling) 与噪声整形公式

- 基础过采样定律:过采样率定义为 。由于噪声能量散布到 ,带内噪声减小,等效 SNR 提升:

- 带噪声整形 (Noise Shaping) 的推导: 对于使用 阶调制器的 Σ-Δ ADC,量化噪声受到 高通滤波整形。带内()的量化噪声总能量被大幅衰减,此时 SNR 的提升规律为: OSR 每翻倍,SNR 提升 。

9 品质因数 (FoM, Figure of Merit) 评价体系

国际学术界(如 ISSCC 和 Murmann Survey)衡量一款 ADC 架构能效的顶级权威标尺,分为两类:

- Walden FoM (): 适用于受限于开关频率而非热噪声的高速/中低精度 ADC。单位为 J/conv-step(焦耳每转换步)。越低越好。

- Schreier FoM (): 适用于受热噪声()物理限制的高分辨率 ADC。因为在高精度下,每提升 1 bit 分辨率,维持同样信噪比所需的电容需增加 4 倍,功耗随之翻 4 倍(而不是 2 倍)。单位为 dB。越高越好。

文章分享

如果这篇文章对你有帮助,欢迎分享给更多人!